To get myself more familiar with the basics of digital design and Verilog, I decided to buy the Basys 3 Artix 7 FPGA development board sold by Diligent. This board comes with a 100 MHz clock, 16 switches, 16 LED’s, 5 buttons, a USB Host, UART Bridge, VGA output, and seven segment displays. Between all of these features, I figured that I would be able to apply what I have learned in my digital logic class and go beyond it to more topics based on my personal interests and future classes.

On this specific page, both videos cover demos and conversation about my time working with designing modules and testbenches related to combination logic, sequential logic, finite state machines, UART communication, and PS2 keyboard receiving interfaces. As a guide, I have been following through the first 9 chapters of the textbook “FPGA Prototyping by Verilog Examples” by Pong P. Chu. This book has helped expand on the syntax that is both synthesizable and not for Verilog, while also explaining useful design practices. I have found this extremely beneficial for modules involving UART, PS2 communication, and complex state machines. Normally in each chapter, the concepts and basic outline of a module will be defined, with extra experiments added at the bottom to expand upon what is given. Through my work over two months, the code presented in these demos are from those experiments. If you are interested in the modules and testbenches I have designed, feel free to access my GitHub repository below!

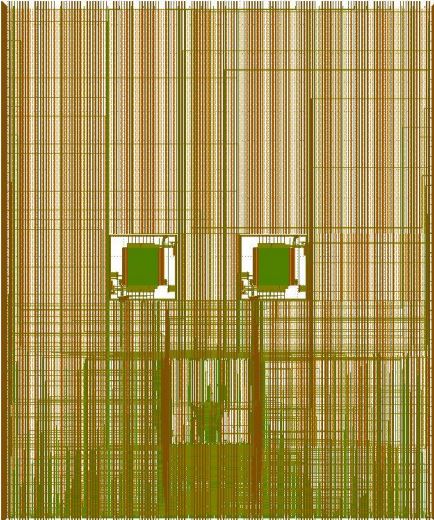

We are able to create our digital ASIC by working through the company eFabless, which is sponsored by Google. The goal of eFabless is to use open-source tools that are freely available to silicon prove both digital and analog ASICs for hobbyists, researchers, and students, who do not have a large pool of resources to take advantage of. Being a senior design team, this was an excellent opportunity to learn more about writing Verilog, using new open-source tools, and designing a chip for fabrication that would come back on an SOC development board. All of the submitted designs are required to be open-source, with the benefit of receiving 5 ASICs that are placed on a development board. eFabless produces their silicon wafers through the U.S. based foundry SkyWater, which takes advantage of 130 nm technology and a standard cell library to fabricate our project. Due to this, we are limited to this fabrication process and the standard cell library that is provided by SkyWater in their 130 nm product development kit. Each project submission is produced on a wafer that houses open-source designs from multiple different projects, enabling eFabless to produce small amounts of ASICs for each team at a reduced cost. While working with open-source tools and a limited production cycle has been difficult through eFabless, they are in a very unique and rare position by offering free digital ASIC fabrication, that is returned on an integrated development SOC board for us to test.

As of December 2023, the project has been completed, and has passed the precheck so that it is ready for submission in the next Multi Project Wafer submission at the Skywater foundry with the 130nm process and open-source PDK. I learned a lot about this process both from utilizing rapidly evolving open-source tools, and working on varying parts of the ASIC design process, such as functional design, verification, and place and route all at different times! This project was extremely valuable and was a great capstone for my senior year of school at Iowa State University.

Documentation

Useful Links

The goal of this project was to learn more about implementing specific components of a processor, and analyzing the performance tradeoffs between each of our three processors. For the software pipeline, we inserted NOP instructions to remove the risk of data and control dependencies within our pipeline. This led to an increased number of instructions, which made our overall execution time larger. As we implemented stalling in the pipeline registers of our hardware pipeline, we were able to reduce the number of instructions used, with the tradeoff of our CPI increasing from a near average of 1. After adding forwarding we were able to reduce the average CPI of our hardware pipeline while retaining a faster maximum clock frequency compared to our single cycle design. By analyzing these choices, we were able to make educated design decisions on how to improve our HW pipeline design, and yield an improved performance compared to our first two processor designs.

Another goal of the project was to take ownership in our required work by taking it a step further with an extra credit project. As mentioned before, we had extra time near the end of the semester, so me and my partner Thomas worked on designing an FPGA wrapper for the Altera DE2 FPGA development board. With this, we were able to combine Verilog code from our previous digital design class, that I also was a teaching assistant for, and a mix of FPGA modules, from the previous library I designed, to make a robust wrapper. It was very satisfying to combine designs for clock dividers, button debouncers, and seven segment display interfaces that had already been extensively tested, and apply them to an interesting and challenging MIPS processor design. This was also a fantastic goal and achievement since we were finally able to see our processor run on real hardware, and not just the required simulations for the course and lab. For more information, please reference the FPGA tab on this page.

Design Reports

- Single Cycle Design Report

- Multistage Pipeline Design Report

- Performance Analysis

- FPGA Wrapper Report

Controls Spreadsheets

To utilize this PMOD, my goal was to create an array of 8x8 pixel ASCII characters, that could be stored or updated as ASCII values. This could be converted from binary, hex, bcd, or scanned through something like UART. It would be very straightforward to convert the values into ASCII, as long as I could keep that ASCII array as a top level input and treat the OLED controller as a hands off display after it is tested. I would also like to be able to use inputs to change the color of the text and background, to make the displays more dynamic based on different states of the logic modules it works with.

As of now, the first semester of senior design has been completed. During this time, we were able to determine our design plan with doctor Duwe, research more about the tools we will be using, and begin testing submodules in our design. Our team decided on a modular design with multiple different functions, including a clock gating module, digital signals processing filter, an external SPI interface, and more. The intent of choosing a modular design was to push the capabilities of the fabrication process at the SkyWater foundry, and see how many working pieces we could receive on our digital ASIC through working with eFabless.

The following requirements are to be followed to interface with the OLED controller:

- The Master driven clock SCK shall have a frequency less than 6.66 MHz

- The Chip Select pin CS to the OLED slave controller must be pulled low before transmission

- Data on the MOSI line will be read on the positive edge of SCK on the OLED Controller

- A command code will force D/C to 0, while a data byte will force D/C to 1

- VCCEN and PMODEN must be set to 1 after an appropriate delay to turn on the OLED controller

- The command code 0xAF must be sent to power ON the display, followed by a 100ms wait

The above requirements are determined based on the reference manual for the SSD1331 OLED display controller and the schematic for the OLEDrgb breakout PMOD from Digilent. This would dictate the turn on sequence for the OLED controller, and lead me to designing a standard write only SPI module, which would handle driving the CS and MOSI pins.

The following requirements were determined by myself to achieve the goal of a fully controllable ASCII display:

- The full range of the display will be utilized, being 96 columns and 64 rows of pixels

- Each ASCII character will have 8 columns and 8 rows, or 64 total pixels

- The ASCII values will be stored as ASCII types, and converted to the 8x8 bit array through a case statement

- The ASCII values will be displayed one at a time, modifying the start and end addresses to display each 8x8 bit block in succession

- The ASCII characters will be displayed row by row, starting at column position 0 and incrementing to the right

- The ASCII text shall be one set color, and the ASCII background shall be another color, as inputs to the OLED Interface controller

The following set of modules were planned to be implemented, to achieve a fully customizable ASCII display in real time:

- Nbit_MOSI_SPI: A shift register will handle transmitting 1 byte of data over MOSI and driving CS, on the negative edge of SCK

- Nbit_MOSI_SPI_Buffer: Another module will load multiple bytes of data and D/C bits to send strings of commands in a row, updating on the positive edge of SCK

- OLED_interface: An OLED Controller module will be created to handle the turn on, turn off, and display states by writing to the byte buffer

- Ascii_font_8x8: Decodes 1 byte ASCII type into 8x8 bit array of pixels, with MSB being the top right pixel, LSB being the bottom left pixel, row by row